- Startseite

- News

- 7-Tage-News

- Linklisten der News

- Newsindex-Übersicht

- AMD RDNA3

- AMD RDNA4

- AMD RDNA5

- Intel Xe

- Intel Battlemage

- Intel Celestial

- nVidia Ada Lovelace

- nVidia Blackwell

- nVidia Rubin

- AMD Zen 4

- AMD Zen 5

- AMD Zen 6

- Intel Raptor Lake

- Intel Meteor Lake

- Intel Lunar Lake

- Intel Arrow Lake

- Intel Panther Lake

- Intel Nova Lake

- Artikel

- Downloads

Hauptlinks

Suchen

Chipfertigung

3

Intel versetzt seinen CEO Pat Gelsinger in den Ruhestand

Intel versetzt seinen CEO Pat Gelsinger in den Ruhestand

Die Nachricht des gestrigen Tages ist natürlich die In-Ruhestand-Setzung von Intels nunmehr vormaligen CEO Pat Gelsinger schon zum 1. Dezember, was Intel etwas lapidar erst am 2. Dezember mitteilte. Interimsmäßig geht es mit zwei Co-CEOs weiter, die Suche nach einem neuen Chef beginnt erst. Augenscheinlich hatte Pat Gelsinger zuletzt das Vertrauen des Intel-Verwaltungsrats verloren und kommt man mit dieser In-Ruhestand-Setzung einer direkten Entlassung vor. Genauere Details hierzu fehlen allerdings und dürfte Intel wohl auch niemals offiziell bekanntgeben. Die allgemeine Vermutung ist, dass der Intel-Verwaltungsrat hiermit auf die finanzielle Katastrophe der Geschäftsergebnisse des dritten Quartals samt dem mageren Ausblick auf die nachfolgende geschäftliche Entwicklung reagierte – sprich, es dürfte primär darum gehen, Intel so schnell wie möglich von den roten Zahlen wegzubekommen. Dafür ist ein Techniker wie Pat Gelsinger vielleicht weniger geeignet und dürften somit vorerst die Pfennigfuchser bei Intel übernehmen – denkbarerweise mit neuen Sparprogrammen.

28

Gerüchteküche: nVidias GB203 könnte auch mittels Durchsägen des GB202-Chips gewonnen werden

Gerüchteküche: nVidias GB203 könnte auch mittels Durchsägen des GB202-Chips gewonnen werden

Aussagen von Twitterer & Leaker 'Kopite7kimi' haben die Diskussion neu angestoßen, wie die beiden Top-Chips von "Gaming-Blackwell" GB202 & GB203 zu verstehen sind. Wie bekannt, trägt der GB202-Chip die glatt doppelte Hardware des GB203-Chips – was immer schon die Vermutung ins Kraut hat schießen lassen, nVidia würde beim GB202 auf ein MultiChip-Konstrukt setzen. Dem gegenüber hatte der Leaker kürzlich aber noch einmal die monolithische Fertigung des GB202-Chips betont. In einem Nachtrag bezeichnete der Leaker den GB202-Chip allerdings auch als "logischerweise" zweimal GB203 entsprechend. Und dies dürfte ganz wörtlich zu verstehen sein: GB202 muß somit wie zwei zusammengepappte GB203 aufgebaut sein – nur wird dies alles zusammen als ein Chip gefertigt und nicht aus zwei Einzelchips kreiiert.

Do we know if GB202 is a MCM or monolithic design?

Quelle: Dalton Mariano @ X am 23. Mai 2024

physically monolithic

Quelle: Kopite7kimi @ X am 23. Mai 2024

Are they some kind of 2 x gb203?

Quelle: CRSC @ X am 27. Mai 2024

Logically.

Quelle: Kopite7kimi @ X am 27. Mai 2024

24

Weiter rasant steigende Kosten für Chipfertigung und Fertigungsanlagen bis hin zum 2nm-Node

Weiter rasant steigende Kosten für Chipfertigung und Fertigungsanlagen bis hin zum 2nm-Node

Ein sehr umfangreicher Artikel seitens Nikkei Asia, welcher eigentlich Chinas Aufholjagd im Bereich der Halbleiterfertigung betrachtet, bietet auch interessante Folien & Diagramme zum Fortschritt der einzelnen wichtigen Halbleiterfertiger wie auch zur bisherigen wie voraussichtlichen Kosten-Explosion bei immer kleineren Chip-Strukturen. Insbesondere letzteres ist interessant, denn hiermit wird für die 2nm-Fertigung ein enormer Kostensprung sowohl bei der reinen Chipfertigung als auch bezüglich entsprechender Chipwerke vorhergesagt. So sollen zwischen 3nm und 2nm die Wafer-Kosten um +51% steigen (berechnet für Apple, zum Start des jeweiligen Nodes), während die Fertigungsanlagen-Kosten um auch noch +42% zunehmen sollen. Dies wäre ein ähnlich teurer erkaufter Fortschritt wie zwischen 7nm und 5m (28nm zu 16nm ist schlecht vergleichbar, da hierbei der 20nm-Node ausgelassen wurde).

6

"Moore's Law" ist nur noch teilweise zu halten

48 Years of Microprocessor Trend Data — entnommen SemiAnalysis

"Moore's Law" ist nur noch teilweise zu halten

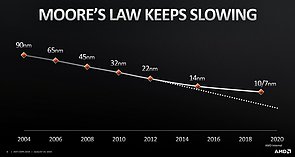

Ein von Halbleiterfertigungs-Zulieferer "Nova Ltd." kommender Artikel bei SemiAnalysis beschäftigt sich mit der Haltbarkeit von "Moore's Law" in einem sehr langfristigen Rahmen, unterteilt in grundverschiedene Phasen von dessen Wirkungsweise. Beachtenswert sind hierbei die verschiedenen Aspekte, unter welchem man jenes "Halbleiter-Gesetz" angesehen hat: Anzahl der CPU-Kerne, Stromverbrauch, Taktrate, Singlethread-Performance und Transistoren-Anzahl werden hierzu angeführt (leider nicht der Fertigungspreis). Interessant ist, dass sich "Moore's Law" bei fast allen diesen Aspekten abschwächt – nur bei der Transistoren-Anzahl nicht, jene geht auch jetzt noch steil nach oben. Aber eigentlich ist damit alles schon gesagt: Der Aufwand (und damit die Kosten) nehmen weiterhin zu, der herauskommende Effekt geht hingegen zurück. Vulgo: Man kann mehr (Transistoren) herstellen, bekommt aber nirgendwo äquivalent mehr (Performance) heraus.

48 Years of Microprocessor Trend Data — entnommen SemiAnalysis

26

TSMCs 3nm-Fertigung wird (erneut) keine Performance-Verdopplung ermöglichen

TSMCs 3nm-Fertigung wird (erneut) keine Performance-Verdopplung ermöglichen

Der Planet 3DNow! und AnandTech berichten zu den technischen Spezifikationen von TSMCs 3nm-Fertigung, welche der derzeit weltweit führende Halbleiter-Fertiger immerhin schon im zweiten Halbjahr 2022 in die Massenfertigung überführen will. Jene soll gegenüber der standardmäßigen 5nm-Fertigung eine Flächenreduktion um -42%, eine Taktraten-Verbesserung um +10-15% sowie eine Stromverbrauchsersparnis von -25-30% bringen (bei Taktrate/Stromverbrauch gilt immer entweder/oder, nicht jedoch gleichzeitig in dieser Höhe). TSMC wird in der Presse dafür ziemlich gelobt, obwohl eigentlich beim Vergleich der Daten zur 5nm-Fertigung auffallen müsste, dass die 3nm-Fertigung einen nochmals kleineren Sprung daherbringt. Wie schon oftmals an dieser Stelle derart genannt, hat TSMC zugunsten der eigenen Roadmap-Durchführung die technischen Fortschritte der jeweiligen NextGen-Fertigungsstufen reduziert – von 3nm zu 5nm ist es eher denn ein "Dreiviertel-Nodesprung" als denn ein üblicher "Fullnode-Sprung".

| Massenfertigung | Vergleich | Flächenbedarf | Taktrate | Stromverbr. | |

|---|---|---|---|---|---|

| TSMC N7 | laufend | N7 vs. N10 | > -37% | ? | < -40% |

| TSMC N7P | laufend | N7P vs. N7 | ±0 | +7% | -10% |

| TSMC N7+ | laufend | N7+ vs. N7 | -17% | +10% | -15% |

| TSMC N6 | laufend | N6 vs. N7 | -18% | ±0 | ±0 |

| TSMC N5 | Q2/2020 | N5 vs. N7 | -45% | +15% | -30% |

| TSMC N5P | 2021 | N5P vs. N5 | ±0 | +5% | -10% |

| TSMC N4 | 2021 | N4 vs. N5 | ? | ? | ? |

| TSMC N3 | H2/2022 | N3 vs. N5 | -42% | +10-15% | -25-30% |

16

USA versuchen Chip-Lieferungen an Huawei per neuer Export-Beschränkungen zu unterbinden

USA versuchen Chip-Lieferungen an Huawei per neuer Export-Beschränkungen zu unterbinden

Golem und CNBC machen auf eine gewichtige Exkalation des US/China-Handelskriegs bzw. des US-Embargos gegenüber Huawei aufmerksam, welche an diesem Freitag in Kraft getreten ist. Danach hat das US-Handelsministerium nunmehr seine früheren Pläne in die Tat umgesetzt und (mit einer Karenzzeit von 120 Tagen für bereits in Fertigung befindliche Produkte) alle Chipfertigung sowie die Ausrüstung zur Chipfertigung unter Export-Beschränkungen gestellt. Somit benötigen Unternehmen, welche die herauskommenden Produkte (Chips) dann an Huawei oder ein Huawei-Tochterunternehmen liefern wollen, nach der Karenzzeit eine entsprechende Lizenz des US-Handelsministeriums. Mittels dieses Druckmittels sind primär den US-Chipfertigungsausrüstern Applied Materials und Lam Research sowie dem US-Halbleiterfertiger Intel zukünftig die Hände gebunden, wenn man an Huawei liefern wollte. Gleichfalls betrifft diese Anordnung aber auch weltweit alle Chipfertiger, welche Chipfertigungs-Anlagen von (jeglichen) US-Herstellern einsetzen – ist aber natürlich primär auf den taiwanesischen Auftragfertiger TSMC gemünzt, wo Huawei massiv fertigen läßt.

26

Simpler Grund der 14nm-Probleme: Intel muß wegen des Wettbewerbs mit AMD nunmehr viel größere Chips anbieten

Simpler Grund der 14nm-Probleme: Intel muß wegen des Wettbewerbs mit AMD nunmehr viel größere Chips anbieten

Der AMD-seitig bereits besprochene Conference Call von Charlie Demerjian mit der Investment-Firma "Susquehanna", welcher in umfangreicher Form auf Reddit niedergelegt wurde, ergeht natürlich vorwiegend zu Intel bzw. Intels aktuellen Problemen. Folgt man dabei den Ausführungen seitens Charlie Demerjian von SemiAccurate, dann wird Intel mehr oder weniger alle seine mittelfristigen Pläne nicht einhalten können, respektive sich die Intel-Roadmap grob um ein Jahr verschieben. Einzurechnen wäre hierbei allerdings, das Charlie durchaus dafür bekannt ist, mit Intel besonders hart ins Gericht zu gehen – sowie gleichzeitig auch der Punkt, das Intel erst kürzlich eine der primären Aussagen über eine Verschiebung der Server-Generation "Ice Lake SP" klar dementiert hat. Wieviel wirklich dran ist an diesen Weltuntergangs-News zu Intel, wird die Zeit zeigen – ganz so schlimm wie berichtet ist es schwer vorstellbar, dies wäre dann wirklich desaströs für Intel. Aber es gibt auch einen beachtenswerten Abschnitt, welcher völlig unabhängig von diesen Roadmap-Widrigkeiten auf den eigentlichen Grund der 14nm-Lieferschwierigkeiten bei Intel eingeht:

In H2 of 2018, the shortages were due to server performance hits over security vulnerabilities.

In December of 2018, they admitted that it was due to increasing die size, which dropped the number of chips that they can produce.

This is due to AMD.

Intel's sweet spot, with 60% of sales, used to be 80-90 mm^2.

AMD core increases drove that up to 125 mm^2, so they lost one third of their production capacity.

Intel's original plan was to have a four core max at 14 nm. That is now 6 to 8 cores, even 10.

Quelle: Charlie Demerjian im Confernce Call mit Susquehanna, niedergeschrieben bei Reddit am 20. Dezember 2019

20

Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

Die Keynote von AMDs CEO Lisa Su auf der laufenden "Hot Chips 31" Konferenz beschäftigte sich ankündigungsgemäß mit Server- und Supercomputer-Themen (PDF der AMD-Präsentation) – und wurf dabei allerdings auch die Frage auf, wie weit man hierbei noch kommt, wenn die neuen Fertigungstechnologien keine so gewaltigen Sprünge wie in der Vergangenheit ermöglich, dafür aber die Kosten pro Chipfläche unterhalb des 14/16nm-Nodes deutlich ansteigen. Hierzu gab es auch wiederum neue Präsentations-Grafiken, welche beispielsweise zwischen 14/16nm und 7nm einen Kostenanstieg von +69% für ein 250mm² großes Die angeben, zwischen 7nm und 5nm dann weitere +33%. Kumulativ sind dies dann im übrigen +125% gegenüber dem 14/16nm-Node – womit auch ein Grund offensichtlich wird, wieso selbiger 14/16nm-Node inzwischen allgemein als langjähriger Standard-Node für die Breite aller möglichen Halbleiter-Produkte angesehen wird. Gewisse Kostensteigerungen hat es früher zwar auch schon gegeben, jene lagen allerdings üblicherweise bei 10-20% pro Node, nicht gleich bei 30-70% pro Node.

13

Intel bringt mit der "Foveros" Technologie seinen eigenen Chiplet-Ansatz

Intel bringt mit der "Foveros" Technologie seinen eigenen Chiplet-Ansatz

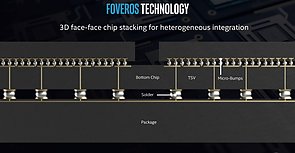

Auf seinem "2018 Architecture Day" hat Intel zeitgleich zur Offenbarung der neuen CPU-Kerne der Glove-Familie die MultiChip-Technologie "Foveros" vorgestellt. Hiermit wird das bisherige Verfahren des Verbaus mehrerer Chips auf einem Package (deutlich) auf die Spitze getrieben: Zum einen können die einzelnen Chips nicht nur nebeneinander, sondern auch übereinander verbaut werden. Zum anderen will man (wie bei AMDs Chiplet-Ansatz bei Zen 2) Chips unterschiedlicher Fertigungstechnologien verbauen können. Intel hat hiermit sozusagen seinen eigenen Chiplet-Ansatz aus der Taufe gehoben – welcher allerdings bereits seinen Vorläufer im Design von Kaby-Lake-G hat, welches wie bekannt einen Intel-Prozessor mit einem AMD-Grafikchip samt HBM2-Speicher auf dasselbe Package bringt. Intel will jenes System nun aber auch rein für den Prozessoren-Bereich adaptieren, ein einfaches Anwendungs-Beispiel wäre ein Kern-Chiplet in einem modernen Fertigungsverfahren, welches auf einem I/O-Chip in einem älteren Fertiungsverfahren sitzt.

5

Der 7nm-Prozeß verdoppelt die Fertigungskosten (auf gleicher Chipfläche)

Der 7nm-Prozeß verdoppelt die Fertigungskosten (auf gleicher Chipfläche)

Beim japanischen PC Watch (maschinelle Übersetzung ins Deutsche) hat man sich mit der Frage beschäftigt, wieso AMD bei Zen 2 auf ein Chiplet-Design setzt. Dabei nennt man als primäre Ursache die steigenden Kosten mit jedem Fertigungsverfahren – wobei der Kostenanstieg vom 14/16nm-Node auf den 7nm-Node besonders drastisch ausfallen soll. So haben sich die Kosten für einen 250mm² großen Chip zwischen 45nm und 14/16nm schon fast verdoppelt, nun aber soll allein der Sprung von 14/16nm auf 7nm eine erneute Kostenverdopplung mit sich bringen. Die hierzu angeführte Folie stammt von AMD selber, dürfte jedoch halbwegs korrekt sein, da AMD die 7nm-Fertigung letztlich auch selber benutzt. Trifft die angeführte Kostensteigerung grob in diesem Rahmen zu, zwingt die 7nm-Fertigung rein von der Kostenseite eigentlich zur Halbierung der Chipfläche (gegenüber vergleichbaren 14/16nm-Chips) – ansonsten würde der herauskommende 7nm-Chip glatt doppelt so teurer herauskommen, was nicht bei jedem damit erstellten Produkt am Markt wirklich darstellbar ist.