- Startseite

- News

- 7-Tage-News

- Linklisten der News

- Newsindex-Übersicht

- AMD RDNA3

- AMD RDNA4

- AMD RDNA5

- Intel Xe

- Intel Battlemage

- Intel Celestial

- nVidia Ada Lovelace

- nVidia Blackwell

- nVidia Rubin

- AMD Zen 4

- AMD Zen 5

- AMD Zen 6

- Intel Raptor Lake

- Intel Meteor Lake

- Intel Lunar Lake

- Intel Arrow Lake

- Intel Panther Lake

- Intel Nova Lake

- Artikel

- Downloads

Hauptlinks

Suchen

20Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

Die Flächen-normierten Fertigungskosten steigen nach dem 14/16nm-Prozeß um +30% pro Node

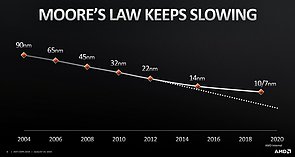

Die Keynote von AMDs CEO Lisa Su auf der laufenden "Hot Chips 31" Konferenz beschäftigte sich ankündigungsgemäß mit Server- und Supercomputer-Themen (PDF der AMD-Präsentation) – und wurf dabei allerdings auch die Frage auf, wie weit man hierbei noch kommt, wenn die neuen Fertigungstechnologien keine so gewaltigen Sprünge wie in der Vergangenheit ermöglich, dafür aber die Kosten pro Chipfläche unterhalb des 14/16nm-Nodes deutlich ansteigen. Hierzu gab es auch wiederum neue Präsentations-Grafiken, welche beispielsweise zwischen 14/16nm und 7nm einen Kostenanstieg von +69% für ein 250mm² großes Die angeben, zwischen 7nm und 5nm dann weitere +33%. Kumulativ sind dies dann im übrigen +125% gegenüber dem 14/16nm-Node – womit auch ein Grund offensichtlich wird, wieso selbiger 14/16nm-Node inzwischen allgemein als langjähriger Standard-Node für die Breite aller möglichen Halbleiter-Produkte angesehen wird. Gewisse Kostensteigerungen hat es früher zwar auch schon gegeben, jene lagen allerdings üblicherweise bei 10-20% pro Node, nicht gleich bei 30-70% pro Node.

Zur Ehrenrettung des 7nm-Nodes muß allerdings gesagt werden, das jener natürlich eigentlich einem doppelten Fullnode-Sprung entspricht – eigentlich steht da noch der 10nm-Node dazwischen, auch wenn selbiger nicht für PC-Produkte benutzt wurde (Intels 10nm-Fertigung entspricht übertragen der 7nm-Fertigung von TSMC und Samsung). Der reale Kostenzuwachs pro Node liegt nach dem 14/16nm-Node somit bei ca. 30% pro Node – was immer noch deutlich mehr ist als die 10-20% vor dem 14/16nm-Node. So oder so summiert sich dies nunmehr viel schneller auf als zu früheren Zeiten: Für eine erste Kostenverdopplung beim vorgenannten Beispiel-Die mit 250mm² Chipfläche brauchte es den Weg vom 45nm-Node zum 14/16nm-Node (Zeitraum: 2009-2016), für die zweite Kostenverdoppelung dann nur noch den Weg vom 14/16nm-Node zum 5nm-Node (Zeitraum: 2016-2021). Diese zweite Kostenverdopplung wird also nicht nur weniger Nodes benötigen, sondern mit fünf anstatt sieben Jahren auch etwas weniger an Zeit – die Flächen-normierte Kostenzunahme in der Halbleiterfertigung zieht zweifellos das Tempo an.

Aus jenen Zahlen ergibt sich im übrigen indirekt auch, das es nach wie vor einen erheblichen Kostenvorteil neuer Nodes pro Transistor gibt: Wenn ein neuer Node auf gleicher Chipfläche (also bei simplifiziert doppelter Transistorenanzahl) 30% mehr kostet, dann liegt pro Transistor eine Ersparnis von immerhin -35% vor. Langfristig und sofern die Produktionsvorbereitungskosten nicht zu hoch sind, lohnt es sich somit durchaus, jedes in Massenfertigung hergestellte Halbleiterprodukt auch in der neuen Fertigung aufzulegen. Das eigentliche Problem liegt eher darin, das man in der Chipbranche kaum jahrelang mit Chips derselben Transistorenmenge hantiert – alles muß immer größer werden und mit (viel) mehr Transistoren ausgestattet werden, und dies in möglichst kurzen Zeiträumen. Der Idealfall ist dabei die Verdopplung der Transistorenmenge zum gleichen Preis (und ohne höheren Stromverbrauch). Von diesem Idealfall entfernen sich die Fertigungsverfahren unterhalb dem 14/16nm-Node immer mehr – und zwingen somit zu höheren Chippreisen oder aber kleineren Fortschritten bei Transistorenmenge und somit dem Performance-Potential.

Ein anderes Problem droht hingegen von der Seite der maximalen Chipgröße, welche ebenfalls über die Zeit angewachsen sind – und nunmehr nahe des herstellbaren Limits kommen (auch wenn sich selbiges sicherlich ebenfalls nach oben verschoben hat). Diese Entwicklung ist ja auch bei Gamer-Grafikchips zu sehen, wo nVidia beim TU102-Chip der GeForce RTX 2080 Ti & Titan RTX mit einer massiven Chipfläche von 754mm² anrückt – eine Größe, die man vor einigen Jahren noch als "nicht herstellbar" angesehen hätte, so oder so aber total grenzwertig ist. Die Problematik liegt darin, das hierbei jetzt schon eigentlich keinerlei Luft mehr für die üblichen Steigerungsraten der Vergangenheit zu sehen ist. Entweder muß man hier einen gewissen Entwicklungsfortschritt abgegeben – oder aber es geht alles in Richtung von MultiChip-Konstrukten, wie bei AMD in Form des Chiplet-Ansatzes und bei Intel mit der Foveros-Technologie schließlich bereits im Einsatz bzw. in Arbeit. So oder so lohnen sich die großen Fortschritte nur noch für Produkt-Segmente, wo man auch bereits ist für große Performancesprünge entsprechend mehr zu bezahlen.

In allen Preis-sensitiven Bereichen (wie dem kompletten Consumer-Markt und auch großen Teilen des Server-Markts) zwingen diese beiden Entwicklungen allerdings dazu, die früher üblichen Performance-Steigerungen pro neuer Generation zukünftig herunterzudämpfen – damit die Kostenlage und somit die Endkundenpreise nicht völlig explodieren. Die Chipfertiger haben auf diese Problematik schon ihre Lösung gefunden, indem deren zukünftige Fertigungsverfahren einfach nicht mehr so große Sprünge hinlegen wie früher noch – es gibt zwar nach wie vor viele neue Nodes, aber deren Differenzen untereinander werden geringer. Die Produkthersteller dürften dieser Tendenz folgen, sprich weiterhin jährlich neue Generationen auflegen, bei jenen aber keine so überzeugenden Performancesprünge wie früher noch zeigen. Speziell für den Grafikchip-Bereich als jenem Consumer-Segment, welches am ehesten an den Limits der Halbleiterfertigung hängt, ist es also in Frage zu stellen, ob zukünftig noch einmal neue Grafikchip-Generationen mit einer nahezu Performance-Verdopplung herauskommen.

Verwandte News

- Intel bringt mit der "Foveros" Technologie seinen eigenen Chiplet-Ansatz

- Der 7nm-Prozeß verdoppelt die Fertigungskosten (auf gleicher Chipfläche)

- Umfrage-Auswertung: Wann werden die ersten 7nm-basierten Gamer-Grafikkarten erwartet?

- GlobalFoundries stoppt die 7nm-Fertigung

- TSMCs 5nm-Fertigung bringt nur unterdurchschnittliche Fortschritte

- Intel bestätigt Whiskey Lake und Cascade Lake für 2018, 10nm-Produkte kommen erst im Jahr 2019

- Umfrage-Auswertung: In welcher Fertigungstechnologie wird nVidias Ampere erwartet?

- AMD wird zukünftig (auch) die neue 12nm-Fertigung von GlobalFoundries nutzen

- Intels Coffee Lake kommt mit drei verschiedenen Prozessoren-Dies: 4C+GT2, 4C+GT3 und 6C+GT2

- nVidia forscht an MCM-basierten Grafikchips