- Startseite

- News

- 7-Tage-News

- Linklisten der News

- Newsindex-Übersicht

- AMD RDNA3

- AMD RDNA4

- AMD RDNA5

- Intel Xe

- Intel Battlemage

- Intel Celestial

- nVidia Ada Lovelace

- nVidia Blackwell

- nVidia Rubin

- AMD Zen 4

- AMD Zen 5

- AMD Zen 6

- Intel Raptor Lake

- Intel Meteor Lake

- Intel Lunar Lake

- Intel Arrow Lake

- Intel Panther Lake

- Intel Nova Lake

- Artikel

- Downloads

Hauptlinks

Suchen

15AMD-Patentantrag zeigt MCM-Grafikchip aus 13 Einzel-Chips

(angeblicher) AMD Navi 4C Design-Entwurf veröffentlicht von Moore's Law Is Dead @ YouTube

AMD-Patentantrag zeigt MCM-Grafikchip aus 13 Einzel-Chips

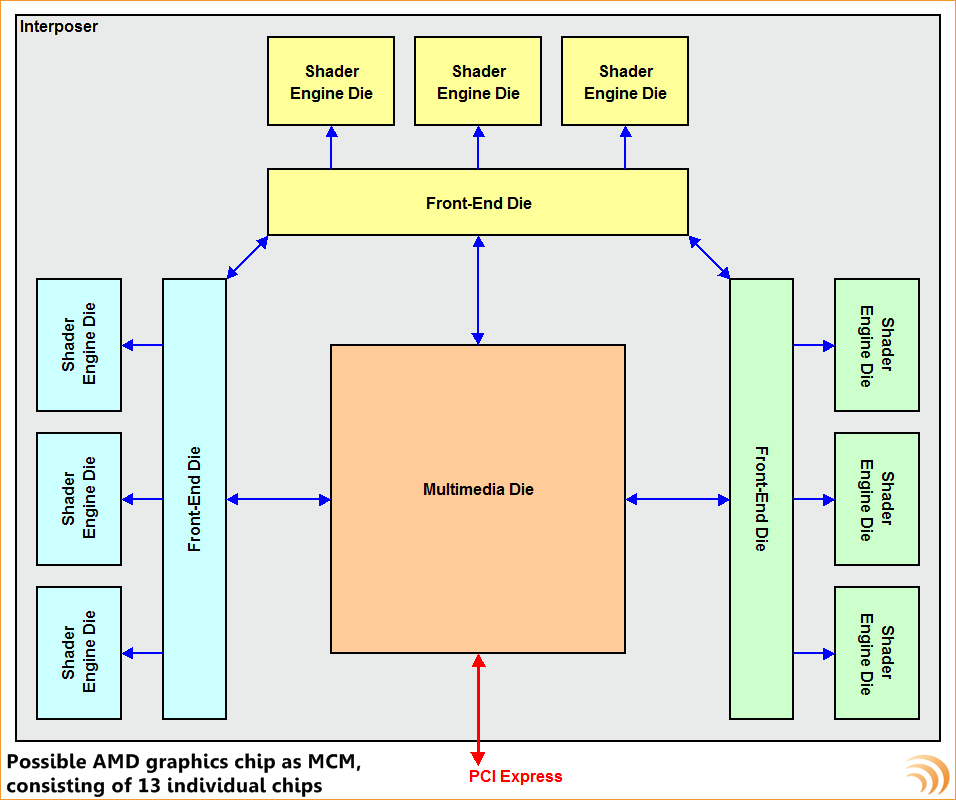

Unter der Woche ist ein AMD-Patentantrag (PDF) aufgetaucht, welcher einen interessanten Grafikchip als MultiChip-Konstruktion bestehend aus (mindestens) 13 Einzel-Chips zeigt. Jener Patentantrag wurde im Dezember 2022 eingereicht und diese Woche veröffentlicht, es handelt sich allerdings noch nicht um ein final erteiltes Patent. Die initiale Grafik zeigt dabei eigentlich schon fast alles, was AMD sich hierbei gedacht hat: Ein Grafikchip bestehend aus drei Front-End-Chips mit jeweils drei Shader-Engine-Chips zuzüglich einem Multimedia-Chip, welcher gleichzeitig wohl auch die Kontrollfunktion innezuhaben scheint. Dabei handelt es sich gemäß dem begleitenden Text auch wirklich um einen Chip zur Berechnung von Spiele-Grafik (explizit werden 3D-Grafik sowie DirectX 11/12 erwähnt) – und somit keine Konstrukt für HPC/AI-Aufgaben.

Faktisch handelt es hierbei um die Bestätigung dessen, dass die früheren Gerüchte zu einer MultiChip-Konstruktion bei RDNA4 korrekt waren. Jene gingen zumindest von einem dreigeteilten Aufbau aus, wobei jeder der drei Teile über angeblich 48 Shader-Cluster verfügen sollte (gemäß anderen Gerüchten gar über 96 CU). Wie bekannt, hat AMD alle größeren RDNA4-Grafikchips und damit auch deren MCM-Ansatz gestrichen, derzeit darf man von RDNA4 bestenfalls Mainstream- und Midrange-Ware erwarten (Navi 44 & 48). Der hier zusehende Ansatz wird somit vorerst nicht realisiert – könnte allerdings von AMD für RDNA5 sehr wohl wieder aktiviert werden. Interessanterweise passt speziell die Aufteilung in mindestens 13 Einzel-Chips sehr gut zu einem letztjährigen Gerücht seitens 'Moore's Law Is Dead':

(angeblicher) AMD Navi 4C Design-Entwurf veröffentlicht von Moore's Law Is Dead @ YouTube

Seinerzeit konnte man sich noch vergleichsweise wenig einen Reim darauf machen, mittels des Patentantrages wird dies nunmehr alles klarer – und auch gut untermauert. Dabei geht die seinerzeitige MLID-Darstellung wohl zu sehr auf die reine Fertigungs-Seite ein, während der Patentantrag sich wenig um die klare Aufteilung der Einzelchips kümmert, sondern eher die logischen Verbindungen untereinander thematisiert. Die folgende, eigenkreiierte Darstellung versucht dies alles noch etwas klarer darstellen, ist aber natürlich auch nur rein schematisch zu verstehen (insbesondere bezüglich der Chipgrößen, welche komplett unbekannt sind). Auch läßt die folgende schematische Darstellung offen, ob eventuell die "Shader-Engine-Dies" auf die "Front-End-Dies" oben drauf geschnallt werden, dies ist für das Verständnis des logischen Aufbaus auch eher zweitrangig.

Klar wird aus dieser Darstellung: Das "Multimedia Die" beinhaltet nicht nur jene Chipteile, welche nur einmalig vorliegen müssen (Bildausgabe, Video-Engine, PCI Express, etc), sondern dürfte natürlich auch die Steuerung des ganzen übernehmen müssen. Hinter dem Multimedia-Die teilt sich der Grafikchip in drei gleichartige Gruppen auf, welche jeweils ein Front-End-Die samt dreier Shader-Engine-Dies beinhaltet, welche dann die eigentliche Arbeit ableisten dürften. Fehlend ist hier offensichtlich der Weg zum Grafikkarten-Speicherinterface zum Holen benötiger Daten sowie Schreiben des entstehenden Bildes. Wo jenes Speicherinterface angebunden wird, ist dem Patentantrag nicht zu entnehmen, es wird irgendwo bei den Front-End-Dies sowie Shader-Engine-Dies sein. Denkbarerweise setzt AMD hier auf weitere Einzel-Dies wie schon bei RDNA3, wo ein "MCM" sowohl Speicherinterface als auch Infinity Cache enthält. Die Anzahl der benutzten Einzel-Dies kann damit also noch weiter steigen.

Der Patentantrag konzentriert sich zudem teilweise stark auf die Funktionalität des (im allerersten Bild zu sehenden) "Mode Selectors": Hiermit kann festgelegt werden, ob alle drei Front-End-Dies zusammenarbeiten, ob sie jeweils getrennt arbeiten oder ob sie in einem hybriden Modus teilweise zusammen und teilweise getrennt arbeiten (eher nur interessant für Chips mit noch mehr Front-End-Dies). Im zweiten Modus soll der MCM-Grafikchip wie als zwei Grafikchips aussehen, im ersten Modus logischerweise wie ein einzelner (mächtiger) Grafikchip. Eine besondere Relevanz ist diesen technischen Möglichkeiten aber derzeit nicht zuzuordnen, denn aus Performance-Sicht besteht die logische Zielsetzung allein im ersten Modus, speziell für die Beschleunigung von Spiele-Grafik. Nicht ganz auszuschließen, dass dieser Teil nur deswegen im Patentantrag steht, damit der Rest nicht all zu trivial daherkommt (und somit vielleicht als "nicht Patent-reif" abgelehnt werden könnte).

Denn natürlich hat der Patent-Antrag bis auf die Idee der starken Chip-Zerstückelung nicht viel zu bieten, eine besondere geistige Schöpfungshöhe ist da weniger vorhanden bzw. liegt die eigentliche Arbeit dann darin, dies funktioniert und tatsächlich auf Performance kommend zu bauen. Für die dabei angesetzten Tricks & Kniffe werden wahrscheinlich kaum Patente aufgelegt, dies würde der Konkurrenz zu viele Detailinfos liefern. Die tatsächlich aufgelegten Patente sind in aller Regel zur juristischen Absicherung gedacht – sowohl gegenüber Patenttrollen als auch gegenüber eventuellen Seiteneinsteigern ins jeweilige Business. AMD & nVidia tun sich mit ihren jeweiligen Patenten hingegen üblicherweise nicht weh – ein solcher Wettstreit würde auch keinen Sieger, sondern vielmehr zwei Verlierer sehen. Intel ist aufgrund seiner Stellung im CPU-Markt (und natürlich auch über seine iGPUs, welche genauso mit Patenten abgesichert werden) der einzig wirklich denkbare Seiteneinsteiger.

Deswegen müssen Patente auch niemals zwingend das wiedergeben, was die Hersteller tatsächlich an kommender Hardware planen. In diesem Fall könnte es aber zugetroffen haben, dass "Navi 41" gemäß AMDs ursprünglicher Planung so ausgesehen haben soll – was auch gut erklären würde, wieso dieses Projekt abgebrochen wurde, nachdem es nicht rechtzeitig zu realisieren war. Doch aufgeschoben ist nicht aufgehoben und so könnte sich die kommende RDNA5-Architektur erneut diesem MultiChip-Ansatz widmen – in dieser Form oder auch abgewandelt, vielleicht auch um neue Detaillösungen modernisiert. Die grundsätzliche Idee, große Grafikchips in Einzelchips aufzubrechen, womit zukünftige Grafikchips dann aus einem Baukasten-System von einzelnen Chiplets zusammengesetzt werden, dürfte uns wohl so lange begleiten, bis jene Idee irgendwann dann auch im Gaming-Bereich realisiert wurde.

Nachtrag vom 16. Juni 2024

Im weiteren Wortlaut des AMD-Patentantrags zum MCM-Grafikchip aus 13 Einzel-Chip werden die bislang fehlenden Speicherinterfaces genannt: Jene sind bei diesem MCM-Konstrukt als Teil der "Front-End-Dies" geplant, ergeben somit keine weiteren Chips. Damit würde dieses MCM-Design wieder weggehen vom RDNA3-Ansatz mit abgetrennten MCDs, welche Speicherinterface und Infinity Cache enthalten. Denkbarerweise hat sich jener RDNA3-Ansatz nicht bewährt, weil zwischen den Einzelchips jeweils größere Interfaces existieren müssen und dies dann den Energieaufwand nach oben treibt (Datentransport ist eine der energieaufwendigsten Dinge innerhalb von Chips). Mit den Speicherinterface innerhalb des "Front-End-Dies" entledigt man sich zumindest dieses Energieaufwands, wenngleich die Anbindung der anderen Einzelchips des MCM-Konstrukts auch wieder mit zusätzlichen Interfaces und damit Energieaufwand verbunden sein sollte.

front end processor die comprises at least one of: a command processor, a graphics register bus hub, a geometry engine, data fabric, a cache, a power controller, a data store, and one or more memory controllers

Quelle: Auszug aus dem US-Patentantrag 18/077,424 (PDF), eingereicht von AMD

Verwandte News

- Die Grafikchip- und Grafikkarten-Marktanteile im ersten Quartal 2024

- Performance-Skalierung von 3DMark TimeSpy und Steel Nomad im Vergleich

- Umfrage-Auswertung: Was sollten AMD & nVidia mit deren nächster Grafikkarten-Generation am dringendsten angehen?

- Umfrage-Auswertung: Wie häufig werden Upscaler in der Praxis eingesetzt?

- Umfrage-Auswertung: Wie häufig wird RayTracing in der Praxis eingesetzt?

- Umfrage-Auswertung: Wie ist der Ersteindruck zu AMDs Radeon RX 7900 GRE?

- Neuer Artikel: Grafikkarten-Verkaufsstatistik Mindfactory Q1/2024

- Neuer Artikel: Grafikkarten-Marktüberblick April 2024

- Gerüchteküche: Hardware-Daten, Chipflächen und eine erste Rechenleistungsangabe zu AMDs Navi 48 & 44

- Gerüchteküche: PlayStation 5 Pro mit drastisch mehr RayTracing-Performance sowie KI-unterstütztem "PSSR" Upscaling