- Startseite

- News

- 7-Tage-News

- Linklisten der News

- Newsindex-Übersicht

- AMD RDNA3

- AMD RDNA4

- AMD RDNA5

- Intel Xe

- Intel Battlemage

- Intel Celestial

- nVidia Ada Lovelace

- nVidia Blackwell

- nVidia Rubin

- AMD Zen 4

- AMD Zen 5

- AMD Zen 6

- Intel Raptor Lake

- Intel Meteor Lake

- Intel Lunar Lake

- Intel Arrow Lake

- Intel Panther Lake

- Intel Nova Lake

- Artikel

- Downloads

Hauptlinks

Suchen

6AMD spricht erste Details zu "Zen 3" an

AMD spricht erste Details zu "Zen 3" an

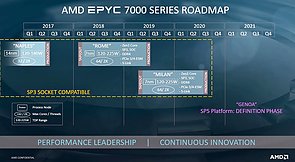

Auf der "UK HPC Advisory Council Conference 2019" hat AMD am 16. September erste Details zur nächstes Jahr anstehenden nächsten Zen-Iteration "Zen 3" verkündet, von der dort gezeigten Präsentation zeugt ein (inzwischen leider schon wieder gelöschtes) YouTube-Video. Der größte Teil der AMD-Präsentation dreht sich zwar um Zen 2 bzw. dessen Server-Variante, in zwei Präsentations-Folien wird jedoch auch auf Zen 3 bzw. dessen Server-Variante "Milan" eingegangen. Mittels dieser bestätigt sich erst einmal, das AMD im laufenden Rennen um immer mehr CPU-Kerne bei Zen 3 vorerst innehalten wird – es bleibt bei maximal 64 CPU-Kernen. Auch die hier und da geäußerten Vermutungen über SMT4 (sprich 4 logische CPU-Kerne pro einem physikalischen CPU-Kern) können als erledigt betrachtet werden, es bleibt bei SMT2 und damit maximal 128 CPU-Threads. Dies läßt AMD natürlich die theoretische Möglichkeit offen, im Desktop- wie im HEDT-Segment dann doch mehr CPU-Kerne als bisher zu bringen, aber für das Server-Segment ist das Maximum damit jetzt schon erreicht.

|

Aller Vermutung nach dürften jedoch im Desktop-Segment bei Zen 3 auch nicht mehr CPU-Kerne anstehen, da der dort benutzte Sockel AM4 hierfür von Anfang an nicht ausgelegt war. An der durchgehenden Weiterverwendung der bisherigen Prozessoren-Sockel AM4 (Desktop), TR4 (HEDT) und SP3 (Server) hängt dann auch der erneute Support von DDR4-Speicher sowie PCI Express 4.0. Der Sprung auf die Unterstützung von DDR5-Speicher samt PCI Express 5.0 dürfte dann erst mit dem nachfolgenden "Zen 4" auf den neuen Sockeln AM5 (Desktop), TR5 (HEDT) und SP5 (Server) erfolgen. Selbiges ist laut der zu sehenden Server-Roadmap im übrigen immer noch in der Definitions-Phase, sprich es wird wohl noch eine ganze Weile daran gearbeitet. Ob es Zen 4 überhaupt noch ins Jahr 2021 schafft, bleibt dabei abzuwarten, denn auch bei Zen 3 braucht AMD wieder etwas mehr als 12 Monate zwischen zwei CPU-Generation. Damit verschiebt sich der jeweilige Launch-Termin immer weiter dem Jahresende zu, womit es irgendwann einmal mehr Sinn machen wird, ein Jahr ganz zu überspringen und direkt im nächsten Januar zu launchen.

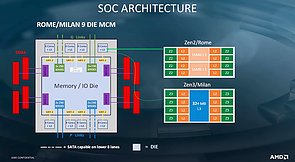

Dies dürfte dann jedoch erst bei Zen 4/5 eine Frage sein, denn Zen 3 scheint noch grob im Sommer 2020 herauszukommen: Die derzeitige Planung sieht für Zen-3-basierte Server-Prozessoren die Mitte des dritten Quartals vor, was den August 2020 ergeben würde. Das die entsprechenden Desktop-Prozessoren zum gleichen Zeitpunkt erscheinen, ist damit nicht gesagt, allerdings durchaus anzunehmen – schließlich sind die Core-Chiplets wiederum von Desktop bis Server dieselben. An jenen Core-Chiplets finden sich dann die größten (derzeit bekannten) Änderungen von Zen 3: AMD läßt die bisherige Grundeinheit CCX (Compute Core Complex) samt deren Einschränkungen prinzipiell fallen. Es finden sich zwar weiterhin 8 CPU-Kerne samt 32 MB Level3-Cache pro Core-Chiplet (CCD, Core Chiplet Die) ein, aber es entfällt die trennende Grenze des CCX mit vormals 4 CPU-Kernen samt 16 MB Level3-Cache. Die Menge an Level3-Cache bei Zen 3 ist allerdings noch nicht final, AMD notierte in der Präsentationsfolie vielsagenderweise "32+ MB" (pro Core-Chiplet).

Jene Auflösung der bisherigen CCX-Unterteilung ergibt mehrere Vorteile: Zuerst eimmal gilt, das dann bei Zen 3 alle diese 8 CPU-Kerne Zugriff auf die kompletten 32 MB Level3-Cache haben werden. Bei Zen 2 war der Zugriff eines einzelnen CPU-Kerns hingegen auf jenen Level3-Cache beschränkt, welcher im eigenen CCX liegt, sprich auf maximal 16 MB (bei Zen1 & Zen+ maximal 8 MB). Gleichfalls fällt natürlich auch die höhere Latenz beim Datenzugriff zwischen zwei CCX komplett weg. Generell dürfte der CCD-Aufbau somit an einigen Stellen einfacher ausfallen können – es entfällt einfach eine Abstraktions-Ebene, das einzelne Core-Chiplet nähert sich damit (bis auf das fehlende Speicher-Interface) immer mehr einer einzelnen regulären CPU an. Sicherlich gehen damit aber auch neue Herausforderungen einher – so wird wahrscheinlich extra Logik erforderlich sein, um das ganze so effizient zu halten, wie es im bisherigen CCX-System war.

Abgesehen von diesen technischen Details bedeutet diese neue Grundeinheit aber vor allem, das sämtliche kleinere Chip-Projekte (wie für den Mobile-Bereich) immer mit mindestens einem 8-Core-Die arbeiten werden – sprich, AMD dürfte spätestens mittels Zen 3 dann auch 8-Kern-Prozessoren im Mobile-Segment anbieten. Dabei spielt es nicht mal eine Rolle, ob jene Mobile-Prozessoren dann schon im Chiplet-Verfahren oder immer noch monolitisch aufgelegt werden – dann selbst bei einem konventionell monolitischen Ansatz wird AMD als Grundeinheit beim CPU-Design immer das neue Zen-3-CCD mit 8 CPU-Kernen ohne jede CCX-Unterteilung verwenden. Vier- und Sechskerner gewinnt man dann aus Salvage-Lösungen, aber die physikalisch vorhandene Hardware wird ab Zen 3 immer aus dem Vielfachen von 8 CPU-Kernen bestehen. Auch etwaige SemiCustom-Lösungen basierend auf Zen 3 würden dann im Design-Baukasten immer jenes 8-Kern-Grundgerüst vorfinden – nicht mehr das von Zen 1, Zen+ und Zen 2 bekannte 4-Kern-Grundgerüst.